RISC-V and Xtensa are two prominent processor architectures known for their customizable instruction sets and efficient performance in embedded systems. RISC-V offers an open standard design enabling broad innovation and flexibility, while Xtensa provides a highly configurable architecture tailored for specific application requirements through Tensilica cores. Explore the strengths and applications of RISC-V and Xtensa to understand which architecture suits your next technology project.

Why it is important

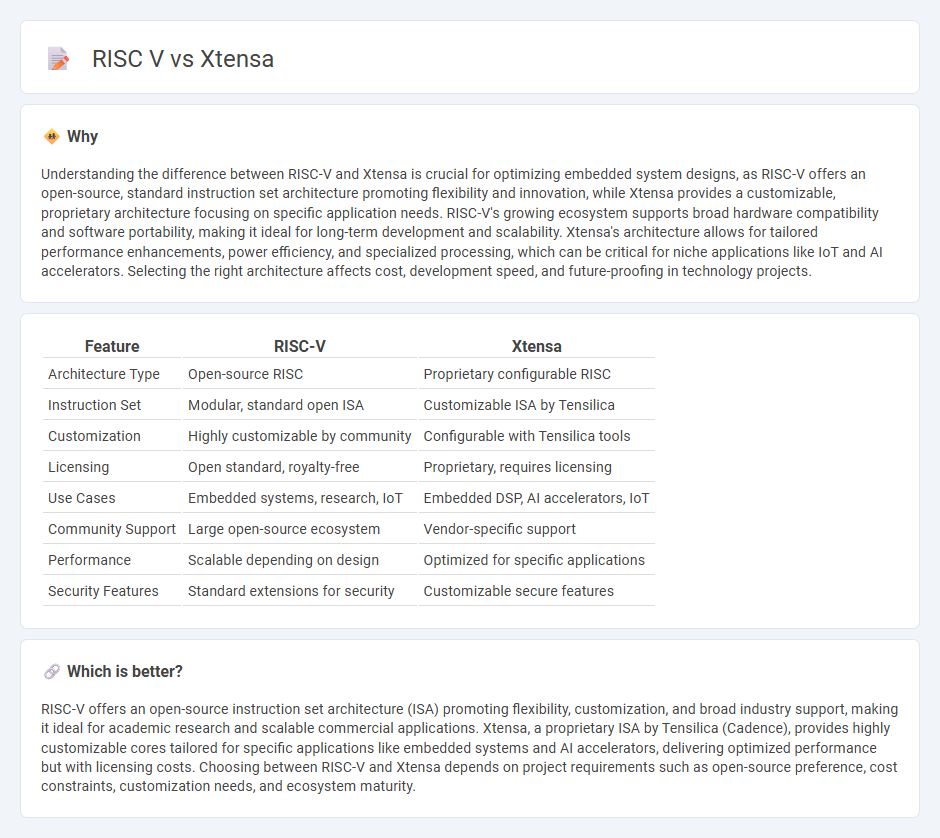

Understanding the difference between RISC-V and Xtensa is crucial for optimizing embedded system designs, as RISC-V offers an open-source, standard instruction set architecture promoting flexibility and innovation, while Xtensa provides a customizable, proprietary architecture focusing on specific application needs. RISC-V's growing ecosystem supports broad hardware compatibility and software portability, making it ideal for long-term development and scalability. Xtensa's architecture allows for tailored performance enhancements, power efficiency, and specialized processing, which can be critical for niche applications like IoT and AI accelerators. Selecting the right architecture affects cost, development speed, and future-proofing in technology projects.

Comparison Table

| Feature | RISC-V | Xtensa |

|---|---|---|

| Architecture Type | Open-source RISC | Proprietary configurable RISC |

| Instruction Set | Modular, standard open ISA | Customizable ISA by Tensilica |

| Customization | Highly customizable by community | Configurable with Tensilica tools |

| Licensing | Open standard, royalty-free | Proprietary, requires licensing |

| Use Cases | Embedded systems, research, IoT | Embedded DSP, AI accelerators, IoT |

| Community Support | Large open-source ecosystem | Vendor-specific support |

| Performance | Scalable depending on design | Optimized for specific applications |

| Security Features | Standard extensions for security | Customizable secure features |

Which is better?

RISC-V offers an open-source instruction set architecture (ISA) promoting flexibility, customization, and broad industry support, making it ideal for academic research and scalable commercial applications. Xtensa, a proprietary ISA by Tensilica (Cadence), provides highly customizable cores tailored for specific applications like embedded systems and AI accelerators, delivering optimized performance but with licensing costs. Choosing between RISC-V and Xtensa depends on project requirements such as open-source preference, cost constraints, customization needs, and ecosystem maturity.

Connection

RISC-V and Xtensa are connected through their roles as customizable processor architectures used in embedded systems and specialized computing applications. RISC-V offers an open standard instruction set architecture (ISA) promoting flexibility and extensibility, while Xtensa provides a highly configurable processor core architecture designed by Tensilica, enabling tailored processing solutions. Both architectures support optimization for specific workloads, driving innovation in areas like IoT, AI, and edge computing.

Key Terms

Instruction Set Architecture (ISA)

Xtensa is a customizable, proprietary ISA developed by Tensilica, offering flexible extensions tailored for specific applications, making it ideal for low-power, embedded systems. RISC-V is an open-source, modular ISA with a simple base and multiple standard extensions, designed for scalability and broad adoption in various computing domains. Explore detailed comparisons to understand which ISA aligns best with your project needs.

Customizability

Xtensa processors offer extensive customizability with configurable instruction sets and user-defined extensions tailored to specific application needs. RISC-V provides an open-source instruction set architecture enabling flexible customization through optional standard extensions and vendor-specific modifications. Explore the detailed comparison to understand which architecture best suits your custom hardware design requirements.

Source and External Links

Xtensa: a configurable and extensible processor - Xtensa is a highly configurable and extensible 32-bit RISC processor core designed for easy integration and customization in system-on-chip designs, featuring a base ISA of about 80 instructions plus optional and custom extensions to optimize performance, power, and code size.

Overview of Xtensa ISA - Xtensa is a post-RISC instruction set architecture that blends RISC efficiency with select CISC features, offers standard 24-bit instructions with optional 16-bit code density, and supports extensive configurability including custom instructions, interrupts, and memory management, all within a Harvard architecture framework.

Tensilica - Tensilica, now part of Cadence, developed the Xtensa family of customizable processor cores, ranging from low-power microcontrollers to high-performance DSP and neural network processors, with automated tools for adding custom instructions and hardware extensions tailored to specific applications.

dowidth.com

dowidth.com